### Universidad Nacional de San Luis Facultad de Ciencias Físico Matemáticas Ingeniería Electrónica con Orientación en Sistemas Digitales

# Diseño de placa Carrier para una plataforma de altas capacidades para computación en el Edge e IA

**Autor** Carlos Ezequiel Duperre

Director Ing. Andrés Miguel Airabella

**Co-Director** Ing. Sergio Fernando Hernandez Velazquez

### Contenidos

- Introducción

- Hardware: Kria K26 SOM

- Objetivos

- Software: KiCad

- Esquemático

- Placa

- Ruteo

- Visualización 3D

- Archivo Gerber

- Trabajos futuros

- Conclusiones

## Introducción

**Ambitious: Edge Al Platform**

Diseño del esquemático y PCB de placa Carrier.

Software y firmware de plataforma.

Sistema operativo y aplicaciones edge.

# Introducción

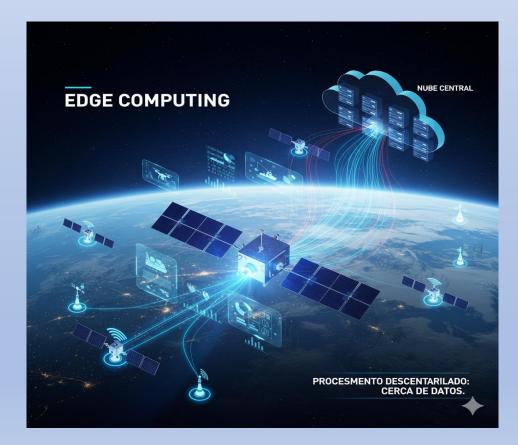

### Computación en el Borde (Edge Computing)

- Baja Latencia

- Respuesta en Tiempo Real

- Filtrado de datos

- Continuidad Operativa

- Seguridad

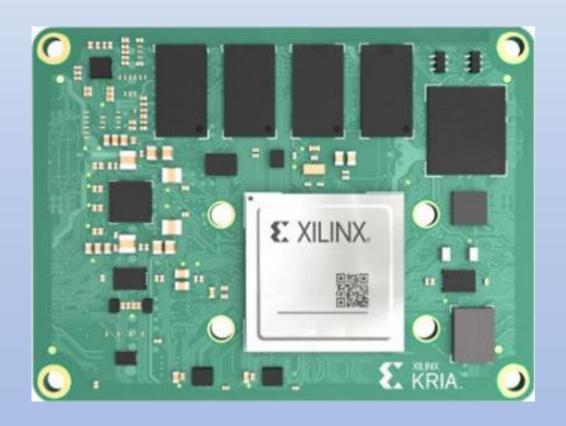

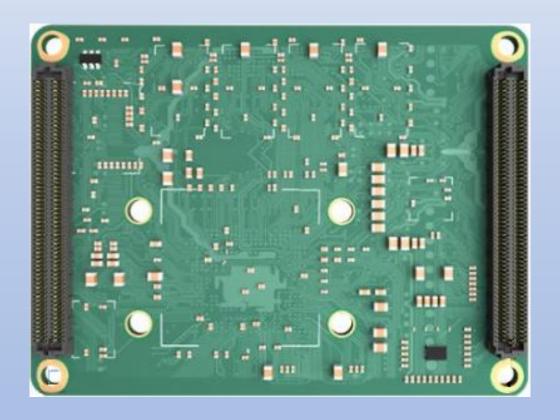

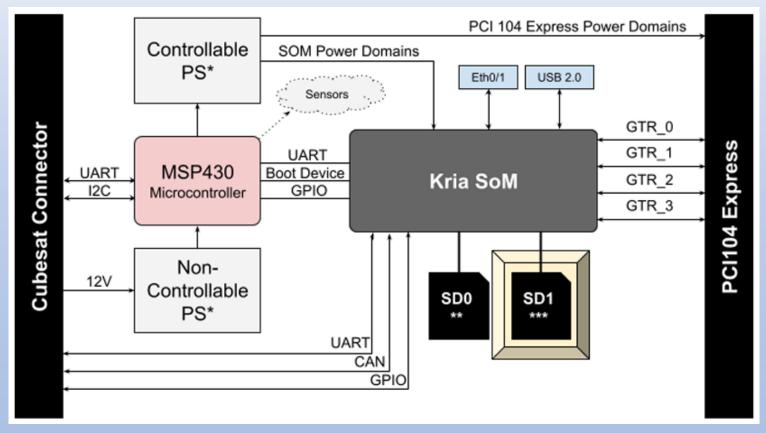

## Hardware: Kria K26 SOM

## Hardware: Kria K26 SOM

Kria KV260 Vision AI AMD/Xilinx

# Objetivos

Este diseño no es hacer la placa de un Arduino!!!

Universidad Nacional de San Luis

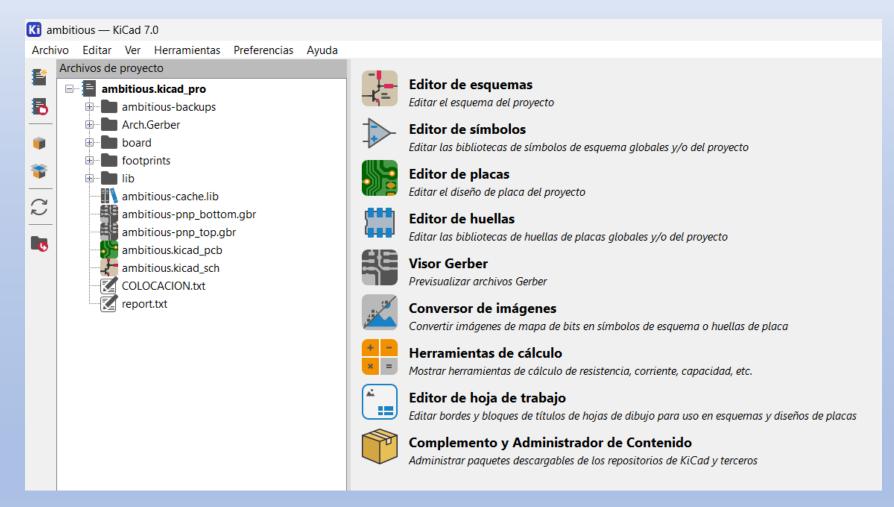

### Software: KiCad

- Software de diseño electrónico de código abierto y gratuito

- Multiplataforma

- Bibliotecas de componentes

- Soporte

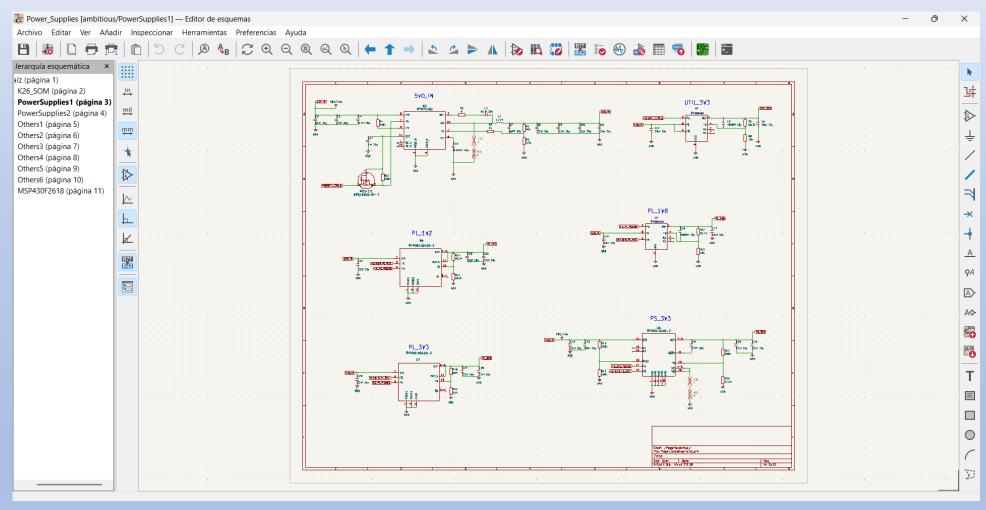

# Esquemático

# Esquemático

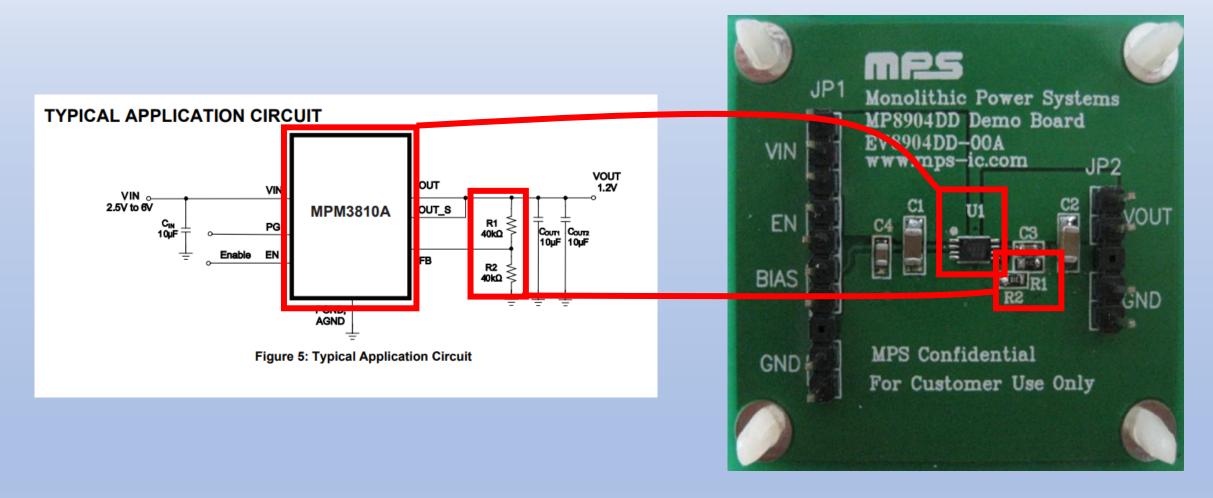

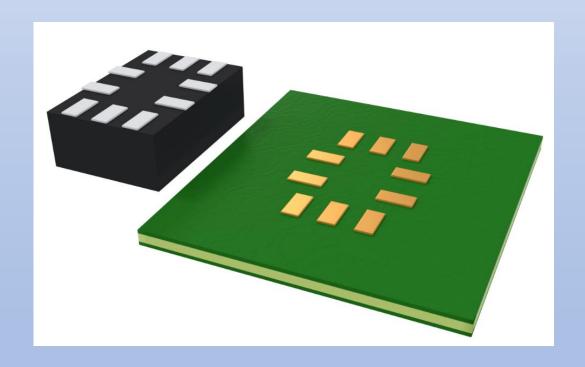

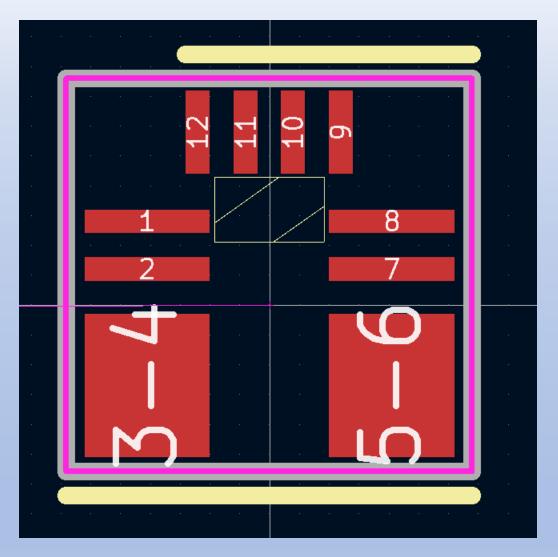

### Huellas

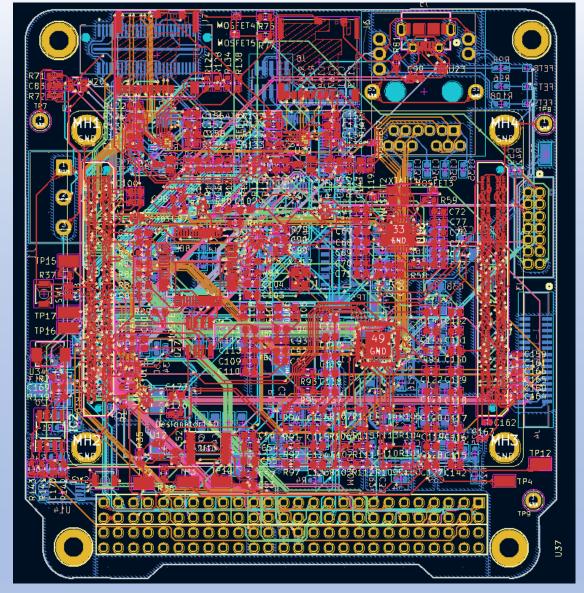

### **Pautas generales**

- Agrupación por bloques

- Selección de componentes

- Longitud de pista

- Trazado de pista

- Interferencias electromagnéticas

- Disipación de temperatura

- Normas IPC (IPC-2221)

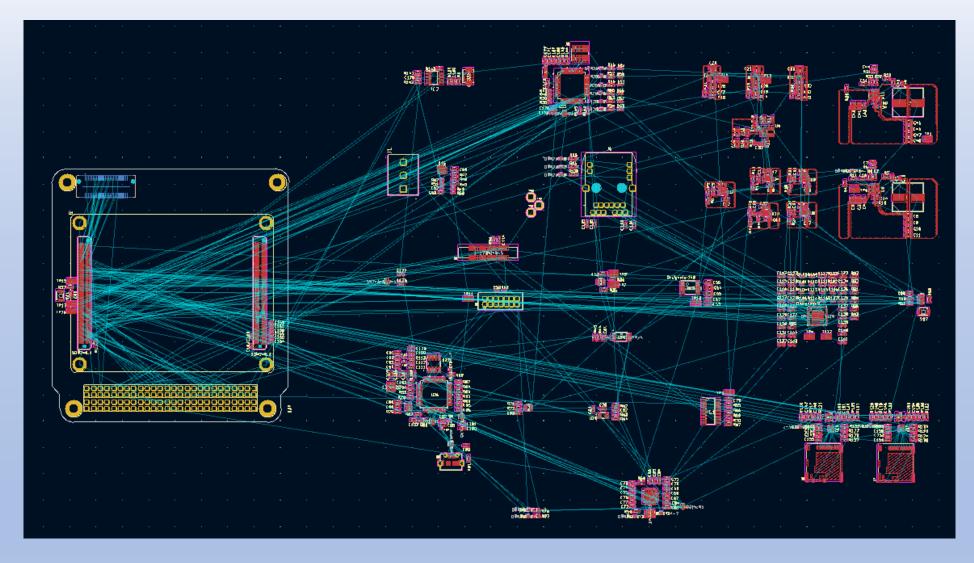

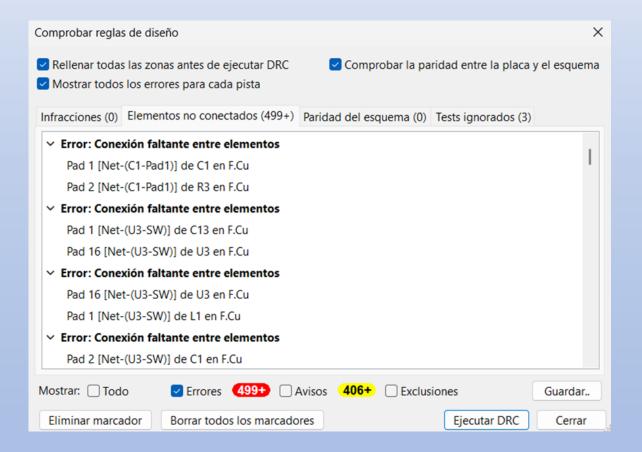

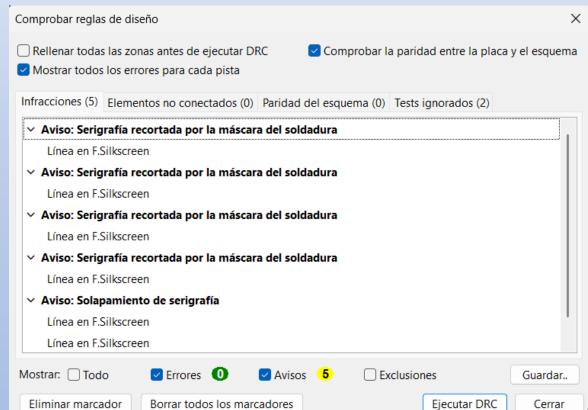

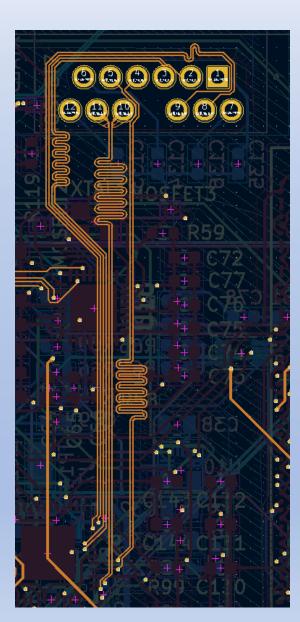

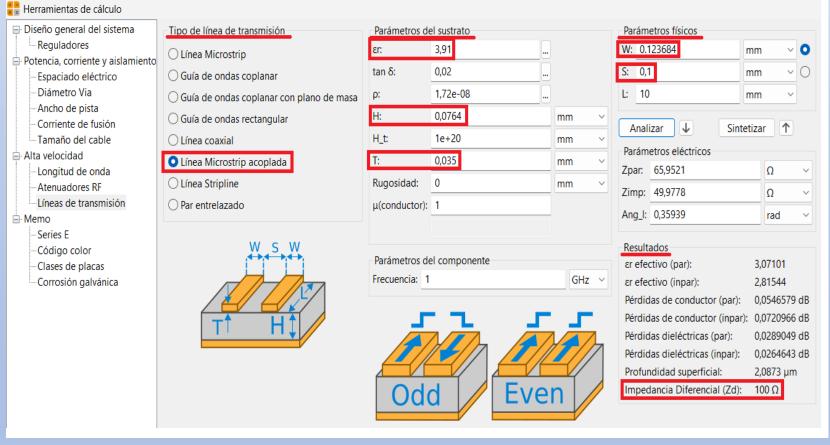

### Ruteo

#### Protocolo Ethernet

## Ruteo

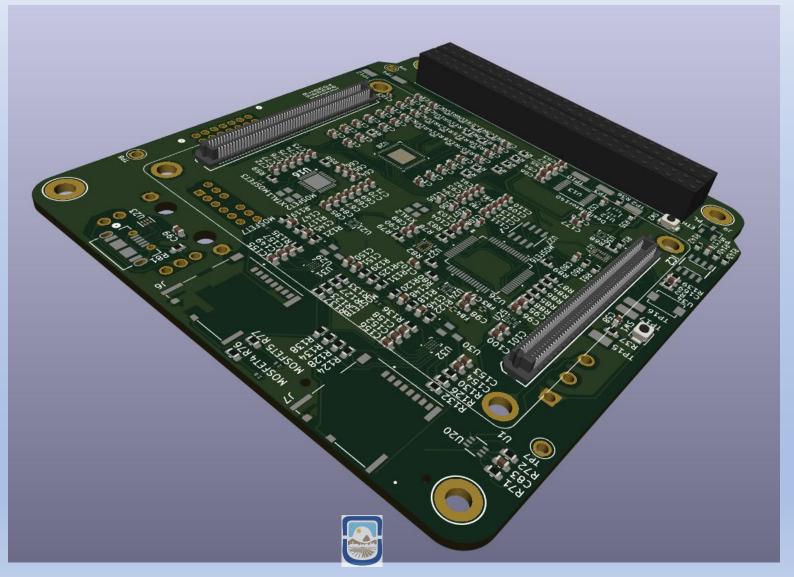

Pads: 2081

Vías: 727

Segmentos de pista: 6060

Redes: 655

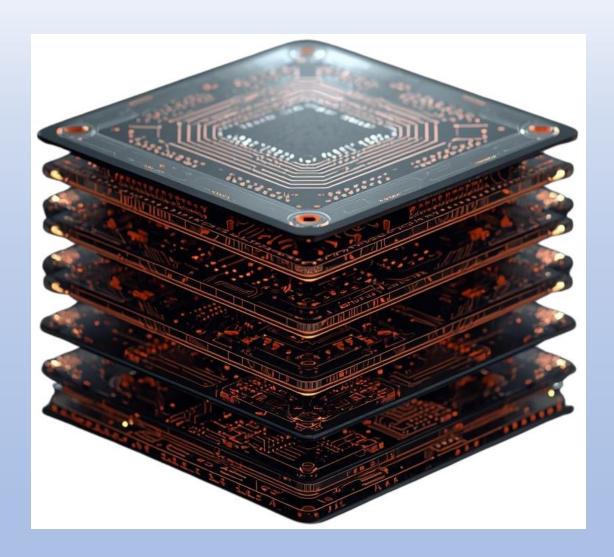

Capas: 8

Componentes: 423

Universidad Nacional de San Luis

# Visualización 3D

Universidad Nacional de San Luis

### Archivo Gerber

### Conclusiones

Objetivos planteados en el Plan de Proyecto Final de carrera:

- 1.Definir y diseñar los componentes que serán parte del circuito de la placa Carrier.

- 2.Realizar el diseño y los cálculos necesarios para las fuentes de alimentación de la placa.

- 3. Definir las huellas de cada uno de los elementos del circuito.

- 4. Determinar la ubicación y las conexiones de todos los elementos del circuito. ✓

- 5.Realizar el diseño del PCB de la placa Carrier. ✓

# ¿Preguntas?

¡Muchas gracias por su atención!

Universidad Nacional de San Luis